EUROGRAPHICS '98 Tutorial

# Rendering and Visualization in Affordable Parallel Environments

Dirk Bartz<sup>†</sup>

WSI/GRIS University of Tübingen

Claudio Silva<sup>‡</sup>, Bengt-Olaf Schneider<sup>§</sup>

IBM T.J. Watson Research Center

#### Abstract

The scope of this full-day tutorial is the use of low and medium-cost parallel environments (less than US \$ 60K) for high-speed rendering and visualization. In particular, our focus is on the parallel graphics programming of multi-processor PCs or workstations, and networks of both.

The current technology push in the consumer market for graphics hardware, small multiprocessor machines, and fast networks is bound to make all of these components less expensive. In this tutorial, attendees will learn how to leverage these advances in consumer hardware to achieve faster rendering by using parallel rendering algorithms, and off-the-shelf software systems.

This course will briefly touch the necessary tools to make basic use of this technology: parallel programming paradigms (shared memory, message passing) and parallel rendering algorithms (including image-, object-, and time- space parallelism). Advantages and issues of the different methods will be discussed on several examples of polygonal graphics and volume rendering.

# **Preliminary Tutorial Schedule**

Part One: Foundations

**Introduction (Bartz/15 minutes)**

Personal Workstations (Schneider/45 minutes)

Parallel Architectures (Bartz/30 minutes)

Parallel Programming (Bartz/60 minutes)

Part Two: Rendering

Parallel Polygonal Rendering (Schneider/45 minutes)

Parallel Volume Rendering (Silva/45 minutes)

Part Three: Case Studies

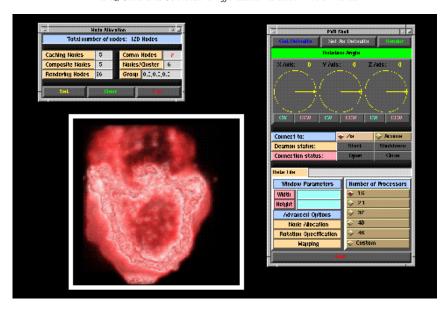

The PVR System (Silva/30 minutes)

Building a Linux-based Parallel Machine (Schneider, Silva/30 minutes)

Q+A (15 minutes)

<sup>†</sup> Email: bartz@gris.uni-tuebingen.de

<sup>‡</sup> Email: csilva@watson.ibm.com

<sup>§</sup> Email: bosch@us.ibm.com

<sup>©</sup> The Eurographics Association and Blackwell Publishers 1998. Published by Blackwell Publishers, 108 Cowley Road, Oxford OX4 1JF, UK and 350 Main Street, Malden, MA 02148, USA.

#### PART ONE

# **Foundations**

#### 1. Introduction

This tutorial gives an introduction into the programming of a variety of affordable parallel environments for parallel rendering and scientific visualization. In our case, we define affordable as less than US\$ 60,000. PCs are covered as well as workstations; polygonal rendering as well as direct volume rendering.

Overall, the tutorial is organized in three parts. The first part discusses foundations of parallel environments. We discuss Personal Workstations - based on a PC architecture, architectures of multi-processor workstations, and parallel programming using the message-passing and the thread paradigm. The second part introduces into parallel rendering techniques. Specifically, we cover parallel polygonal rendering and parallel direct volume rendering.

In the last part of our tutorial two case studies will be presented. The first case study describes PVR, a parallel rendering system exploiting the message-passing programming paradigm. In the second case study, we discuss a LINUX-based parallel graphics environment. However, the material of the last case study could not be included at press deadline please check the following URL for recent updates of our tutorial:

http://www.gris.uni-tuebingen.de/~bartz/ EG\_Tutorial/

Our Eurographics'98 tutorial concludes with a question and answer session.

#### 2. Personal Workstations

The advent of powerful processors and robust operating systems for PCs has sparked the creation of a new type of compute platform, the Personal Workstation (PWS). Several vendors, including Compaq, HP, and IBM, sell systems that are targeted at market segments and applications that till only a few years ago were almost exclusively the domain of UNIX-based technical workstations<sup>102</sup>. Such applications include mechanical and electrical CAD, engineering simulation and analysis, financial analysis, and digital content creation (DCC). PWSs are rapidly adopting many features from UNIX workstations, such as high-performance subsystems for graphics, memory, and storage, as well as support for fast and reliable networking. This development creates the opportunity to leverage the lower cost of PWSs to attack problems that were traditionally in the domain of highend workstations and supercomputers. We will start with an overview of the state of the technology in PWSs and their utility for building parallel rendering systems. Then we will discuss how to improve parallel rendering performance by

enhancing PWS subsystems like disks or network connections like disks or

#### 2.1. Architecture

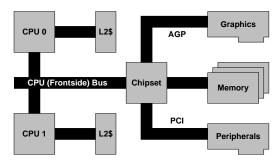

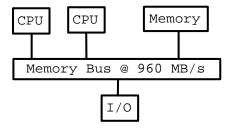

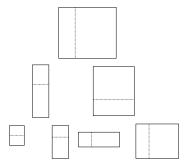

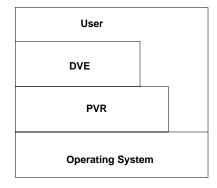

In accordance with the intended application set, PWSs constitute the high-end of the PC system space. Figure 1 shows the architecture of a typical Personal Workstation.

Figure 1: Architecture of a PWS.

The system contains one or two Pentium II processors, large L2 caches (up to 512 kBytes) and main memory (32 MBytes up to several GBytes). If configured with multiple CPUs, the system acts as a symmetric multiprocessor (SMP) with shared memory. As is well known, shared memory architectures have only limited scalability due to finite access bandwidth to memory. Current PWSs only support dual-processor configurations.

The chipset connects the main processor(s) with other essential subsystems, including memory and peripherals. Among the techniques employed to improve the bandwidth for memory accesses are parallel paths into memory<sup>2</sup> and faster memory technologies, e.g. Synchronous DRAM (SDRAM)<sup>58</sup>. Intel has announced that its next generation processor will use Rambus (RDRAM) technology to increase the available memory bandwidth.

The graphics adapter is given a special role among the peripherals due to the high bandwidth demands created by 3D graphics. The Accelerated Graphics Port (AGP)<sup>3</sup> provides a high-bandwidth path from the graphics adapter into main memory. The AGP extends the basic PCI bus protocol with higher clock rate and special transfer modes that are aimed at supporting the storage of textures and possibly z-buffers in main memory, thus reducing the requirements for dedicated graphics memory.

The graphics adapter itself supports at least the OpenGL functionality for triangle setup, rasterization, fragment processing<sup>13</sup> as well as the standard set of 2D functions supported by Windows. Currently, most low-end and midrange graphics adapters rely on the CPU to perform the geometric processing functions, i.e. tessellation of higher-order primitives, vertex transformations, lighting and clipping. However, a new class of high-end PC graphics adapters

| Integer performance:        | 570 MIPS       |

|-----------------------------|----------------|

| Floating point performance: | 220 MFLOPS     |

| Memory bandwidth:           | 140 MBytes/sec |

| Disk bandwidth:             | 13 MBytes/sec  |

**Table 1:** Approximate peak performance data for a Personal Workstation.

is emerging that implement the geometry pipeline in hardware. Hardware-supported geometry operations are important because rasterizers reach performance levels (several million triangles/sec and several 10 million pixels/sec) that cannot be matched by the system processor(s). Also, geometry accelerators can usually provide acceleration more economically than the CPU, i.e. lower \$/MFlops, while freeing the CPU for running applications. However, geometry accelerators will only deliver significant improvements to application performance if the application workload contains a large portion of graphics operations. Many applications (and application-level benchmarks) contain only short bursts of graphics-intensive operations.

Balancing the system architecture requires fast disk, e.g. 10,000 rpm SCSI disk drives, and networking subsystems, e.g. 100 Mbit/sec or 1Gbit/sec Ethernet.

#### 2.2. Parallel Configurations

For the purposes of parallel rendering we will be considering two forms of parallelism: tightly coupled processors in a SMP configuration (as shown in Figure 1) and a cluster of workstations connected over networks. While in a single-processor machine CPU performance is often the most important factor in determining rendering performance, parallel configurations add specific constraints to the performance of parallel rendering algorithms. For SMP workstations, the performance is affected by memory and disk bandwidth. For workstation clusters, the disk and network bandwidth are the most important parameters influencing the rendering performance. The next section provides concrete values for these parameters.

#### 2.3. Performance

To illustrate the performance that can be expected from a PWS we provide approximate performance data in Table 1.

These data were measured with an in-house tool on a preproduction workstation configured with a Pentium II processor running at 400 MHz, 512 KBytes of L2 cache, Intel 440BX chipset, 256 MBytes of 100 MHz SDRAM system memory and a 9 GByte IDE disk. The system ran Windows NT 4.0 with Service Pack 3. Note that many factors affect the actual performance of workstations, amongst them BIOS level, memory architecture and core logic chipset.

**Table 2:** Peak bandwidth between Personal Workstations for different LAN technologies.

We have also conducted measurements of networking performance using various local area network technologies (Table 2). These measurements consisted of transferring large data packets and used the TCP/IP stack that is part of Windows NT 4.0. Note that the observed bandwidth for Gigabit-Ethernet is far below the expected value. A likely source for this shortfall is inefficiencies in the implementation of the TCP/IP stack and the resulting high CPU loads. It is well known that such inefficiencies can result in severe performance degradations<sup>30</sup> and we expect that a better TCP/IP stack would raise the transfer rate.

#### 2.4. PWS Market Trends

So far we have reviewed technical characteristics of PWSs. When selecting a workstation platform technical issues are but one factor.

The developments in the PWS market reflect the PWS's dual-inheritance from Unix workstations and PCs.

As the NT workstation markets matures the price gap between the best performing systems and the systems with best price-performance appears to be closing. This is a known trend know from the desktop PC market which has turned into a commodity market. The PWS market is assuming characteristics of a commodity market with surprising speed, i.e. most products are very similar and have to compete through pricing, marketing and support offerings.

At the same time, PWSs remain different from desktop PCs – and are similar to Unix workstations – in that application performance (in contrast to servicability and manageability) is the primary design and deployment objective. Most purchasing decisions are heavily based on the results in standard and customer-specific application benchmarks.

A particularly interesting question is whether PWSs offer inherently better price-performance than traditional Unix workstations. Over the period that both workstation types participated in the market (1996-1998), NT workstations as a whole have consistently delivered better price-performance than Unix workstations for standard benchmarks. Only recently (mid 1998) Unix workstation are beginning to reach the same price-performance levels. It is unclear whether this constitutes a reversal of the earlier trend or whether the gap will be restored when Intel delivers its next generation processors. Another explanation for the narrowing of

Token Ring 16 Mbit/sec: 14-15 Mbit/sec Ethernet 10 Mbit/sec: 7-8 Mbit/sec Ethernet 100 Mbit/sec: 90 Mbit/sec Ethernet 1 Gbit/sec: 120 Mbit/sec

this gap is that NT workstations are starting to include highperformance subsystems that are required for balanced systems (see below).

# 2.5. Building Parallel Renderers from Personal Workstations

Parallel rendering algorithms can be implemented on a variety of platforms. The capabilities of the target platform influence the choice of rendering algorithms. For instance the availability of hardware acceleration for certain rendering operations affects both performance and scalability of the rendering algorithm.

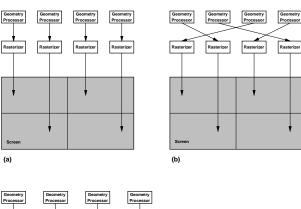

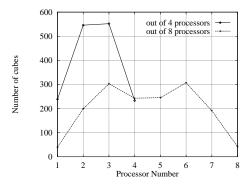

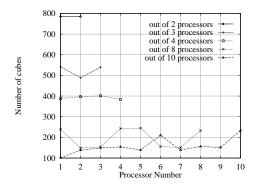

Several approaches to implementing parallel polygon rendering on PWSs with graphics accelerators have been investigated by Schneider<sup>104</sup>. It should be noted that this analysis does not consider pure software implementations of the rendering pipeline; rasterization was assumed to be performed by a graphics adapter.

This is in contrast to software-only graphics pipelines. Such approaches lead to more scaleable rendering systems, even though both absolute performance and price-performance are likely to be worse than the hardware-accelerated implementation. In a paper by Whitman<sup>125</sup>, parallel software renderers have shown close to linear speedup up to 100 processors in a BBN Butterfly TC2000 even though the absolute performance (up to 100,000 polygons/sec) does not match the performance available from graphics workstations of equal or lower cost. However, software renderers offer more flexibility in the choice of rendering algorithms, e.g. advanced lighting models, and the option to integrate application and renderer more tightly.

Following the conclusions from Schneider<sup>104</sup> we will now look at the various subsystems in a PWS that may become a bottleneck for parallel rendering. In part, PWSs have inherited these bottlenecks from their desktop PC ancestors. For example, both memory and disk subsystems are less sophisticated than those of traditional workstations. We will also discuss the merit of possible improvements to various subsystems with respect to parallel rendering performance.

Applications and Geometry Pipeline. As pointed out above, CPU portion of the overall rendering time scales well with the number of processors. Therefore, it is desirable to parallelize rendering solutions with a large computational component. Advance rendering algorithms such as advanced lighting algorithms or ray-tracing will lead to implementations that scale to larger numbers of processors.

*Processor.* Contrary to initial intuition, the performance of CPU and rasterizer does not significantly influence the overall rendering performance. Therefore, parallel rendering does not benefit from enhancements to the CPU, such as by higher clock frequency, more internal pipelines or special instructions to accelerate certain portions of the geometry

pipeline. However as stated earlier, faster CPUs may benefit the applicationSs performance.

*Memory Subsystem.* Currently, memory bandwidth does not limit rendering performance as much as disk and network performance. We expect that memory subsystems will keep increasing their performance over time and retain their relative performance compared to disks and networks. Therefore, more sophisticated memory subsystems, like <sup>2</sup>, will not improve parallel rendering performance.

*Disk Subsystem.* The disk subsystem offers ample opportunity for improvements over the standard IDE or SCSI found in todayŠs PWSs. Faster disk subsystems, e.g. SSA¹ or RAID 0 (disk striping), can be used to alleviate this problem.

Graphics Subsystem. In workstation clusters the use of graphics accelerators with geometry accelerators can be beneficial. For applications with mostly static scenes, e.g. walkthroughs or assembly inspections, the use of retained data structures like display lists can reduce the bandwidth demands on system memory as geometry and lighting calculations are performed locally on the adapter. In SMP machines or for single-frame rendering faster graphics hardware will not provide large rendering speed-ups.

*Network.* In clusters, a slow network interconnect can become the dominant bottleneck. Increasing the network bandwidth by an order of magnitude will alleviate that problem. As stated above, current shortcomings of the protocol implementations prevent full realization of the benefits of Gigabit-Ethernet under Windows NT. Alternative technologies, like Myrinet<sup>36</sup> promise higher sustained bandwidth than Ethernet. However, these technologies are either not available under Windows NT or have not yet been developed into a product. Prototype implementations under Unix (Linux) have demonstrated the advantages of such networks.

#### 2.6. Conclusion

As Personal Workstations are emerging as an alternative to traditional workstations for technical applications they are frequently considered as building blocks for affordable parallel rendering.

Even though PWS are used for parallel rendering in at least one commercial rendering package<sup>53</sup>, its actual implementation is hampered by the lack of efficient networking technologies and insufficient disk performance. Improving these subsystems is possible but will result in more expensive systems, eliminating some of the perceived cost advantage of PWS over traditional workstation.

# 3. Parallel Architectures

In this Section, we discuss general aspects of parallel environments. Although our tutorial covers PCs and workstations, we will focus in this Section only on workstation

environments. However, most of the information on software aspects (message passing, process communication, and threads) is applicable to all UNIX environments (e.g. Linux).

The following Sections will discuss the different parallel approaches, architectures, and programming models for parallel environments.

#### 3.1. Parallel Approaches

Three basic approaches are available for parallel environments. The first approach connects different computers via a network into a cluster of workstations (or PCs). On each individual computer processes are started to perform a set of tasks, while communication is organized by exchanging messages via UNIX sockets, message passing (e.g. PVM), or - more recently - via the Internet. We call this type a loose coupled system, sometimes referred as a distributed processing system.

The second approach consists of a single computer, which contains multiple processing elements (PE which actually are processors). These processing elements are communicating via message passing on an internal high-speed interconnect, or via memory. This type is called a tight coupled system. In contrast to the first approach, communication is faster, usually more reliable, and - in the case of a shared memory system - much easier to handle. However, depending of the interconnection system, the number of processing elements is limited.

The third basic approach is a fusion of the first two approaches. We generally can combine tight or loose coupled systems into a hyprid coupled system. However, in most cases we will loose the advantages of a tight coupled system.

# 3.2. Taxonomy

Flynn developed a taxonomy to classify the parallel aspects of the different (more or less) parallel systems. However, this taxonomy actually only applies to tight coupled systems.

Flynn distinguishes two basic features of a system, the instruction stream (I) - which is code execution - and the data stream (D) - which is the data flow. These features are divided into a single (S) or multiple stream (M). In a single instruction stream, only one instruction can be individually performed by a set of processors, while a multiple instruction stream can perform different instructions at the same time. If we have a single data stream, only this data can be computed or modified at the same time. With a multiple data stream, more than one data element can be processed.

Overall, we have four different types of parallel processing:

SISD - is the standard workstation/PC type. A single instruction stream of a single processor is performing a task on a single data stream.

- SIMD is the massively-parallel, or array computer type. The same instruction stream is performed on different data. Although a number of problems can easily mapped to this architecture (e.g. matrix operations), some problems are difficult to solve with SIMD systems.

Usually, these systems cost hundreds of thousands of US\$ one of the reasons these machines are not covered by this

- MISD is not a useful system. If multiple instructions are executed on a single data stream, it will end up in a big mess. Consequently, there are no computer systems using the MISD scheme.

- MIMD is the standard type of a parallel computer. Multiple instruction streams perform their task on their individual data stream.

#### 3.3. Memory Models

tutorial.

Many aspects of parallel programming depend on the memory architecture of a system, and many problems arise from a choosen memory architecture. The basic question is if the memory is assigned to the processor level, or if the memory is assigned on system level. This information is important for the distribution of a problem to the system. If all memory - except caches - is accessible from each part of the system - memory is assigned on system level, we are talking of a shared memory system. In case the individual processing elements can only access their own private memory - memory is assigned on processor level, we are talking of a distruted memory system. Shared memory systems are further divided into UMA (Uniform Memory Access) systems (not interchangeable with Uniform Memory Architecture), and into NUMA (Non-Uniform Memory Access) systems.

#### 3.3.1. Distributed Memory Systems

In distributed memory systems, the memory is assigned to each individual processor. At the beginning of the processing, the system is distributing the tasks and the data through the network to processing elements. These processing elements receive the data and their task and start to process the data. At some point, the processors need to communicate with other processors, in order to exchange results, to synchronize for periphery devices, and so forth. Finally, the computed results are sent back to the appropriate receiver and the processing element waits for a new task. Workstation clusters fit into this category, because each computer has its individual memory, which is not accessible from its partner workstations within the cluster. Furthermore, each workstation can distribute data via the network.

Overall, it is important to note that communication in a distributed memory system is expensive. Therefore, it should be reduced to a minimum.

#### 3.3.2. Shared Memory Systems

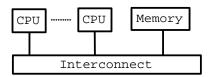

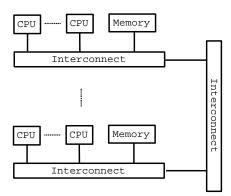

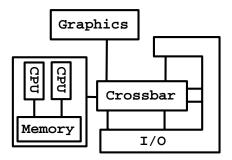

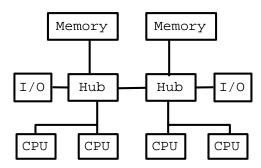

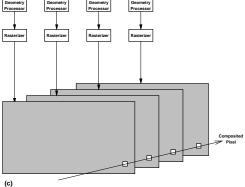

UMA systems contain all memory<sup>†</sup> in a more or less monolithic block. All processors of the system access this memory via the same interconnect, which can be a crossbar or a bus (Figure 2). In contrast, NUMA systems are combined of two or more UMA levels which are connected via another interconnect (Figure 3). This interconnect can be slower than the interconnect on the UMA level. However, communication from one UMA sub-system to another UMA sub-system travels through more than one interconnection stage and therefore, takes more time than communication within one UMA sub-system.

Figure 2: Uniform Memory Access

If UMA systems have a better communication, why should we use NUMA systems? The answer is that the possibilities to extend UMA systems are limited. At some point the complexity of the interconnect will rise into infinity, or the interconnect will not be powerfull enough to provide sufficient performance. Therefore, a hierarchy of UMA subsystems was introduced.

Figure 3: Non-Uniform Memory Access

#### 3.4. Programming Models

So far, we jave introduced different approaches of parallelization (loose coupled or distributed processing, tight-coupled processing, and hyprid models of loose- or tight-coupled processing) and different memory access architectures. In this Section, we add two different paradigms for the programming of parallel environments.

#### 3.4.1. Message-Passing

This programming paradigm connects processing entities to perform a joined task. As a matter of principle, each processing entity is an individual process running on a computer. However, different processes can run on the very same computer, especially, if this computer is a multi-processor system. The underlying interconnection topology is transparent from the users point of view. Therefore, it does not make a difference in programming, if the parallel program which communicates using a message-passing library runs on a cluster of workstations, on a distributed memory system(e.g. the Intel Paragon), or on a shared-memory system (e.g. the HP Convex/SPP).

For the general process of using a message-passing system for concurrent programming it is essential to manually split the problem to be solved into different more or less independant sub-tasks. These sub-tasks and their data are distributed via the interconnect to the individual processes. During processing, intermediary results are sent using the explicit communication scheme of message-passing.

Considering the high costs using the network, communication must be reduced to a minimum. Therefore, the data must be explicitly partitioned. Finally, the terminal results of the processing entities are collected by a parent process which returns the result to the user.

Their are several message-passing libraries around. However, most applications are based on two standards, which are explained in Section 4.2 and Section 4.1; the PVM3 library (Parallel Virtual Machine) and the MPI standard (Message Passing Interface).

#### 3.4.2. Threading

A more recent parallel programming paradigm is the thread model. A thread is a control flow entity in a process. Typically, a sequential process consists of one thread; more than one thread enable a concurrent (parallel) control flow. While the process provides the environment for one or more threads - creating a common address space, a synchronization and execution context - the individual threads only build a private stack and program counters. The different threads of a single process communicate via synchronization mechanisms and via the shared memory.

Sometimes the concept of light-weight processes (LWP) is used as a synonym for threads. However, a LWP actually is a physical scheduling entity of the operating system, in a way the physical incarnation of the logical concept of a thread.

In contrast to message passing, threading is only possible on multi-processor systems. Moreover, multi-processor systems need a shared-memory architecture, in order to provide the same virtual address space.

$<sup>^{\</sup>dagger}$  We are talking of main memory. Processor registers, caches, or harddiscs are not considered as main memory.

<sup>‡</sup> There are some thread models which run on distributed mem-

Besides easy communication and data exchange using the shared memory, switching between different threads is much cheaper/faster than switching between individual processes. This is due to the shared address space, which is not changed during a thread switch.

Basically, there are three different kinds of implementations for threads. There is a user thread model, a kernel thread model, and a mixed model. The user thread model is usually a very early implementation of a thread package. All thread management is handled by the thread library; the UNIX kernal only knows the process, which might contain more than one thread. This results in the situation that only one thread of a process is executed at any particular time. If you are using threads on a single processor workstation, or your threads are not compute-bound, this is not a problem. However, on a multi-processor system, we do not really get a concurrent execution of multiple threads of one process. On the other hand, this implementation model does not require a modification of the operating system kernel. Furthermore, the management of the threads does not require any kernel overhead. In Pthread terminology, this model is called all-toone-scheduling.

In contrast to user threads, each kernel thread (on Solaris systems a kernel thread is called a light-weight process, on SGI systems a sproc) is known to the operating system kernel. Consequently, each kernel thread is individually schedulable. This results in a real concurrent execution on a multiprocessor, which is especially important for compute-bound threads. However, allocation and management of a kernel thread introduces significant overhead to the kernel, which eventually might lead to a bad scaling behaviour. Pthread terminology denotes this model to be one-to-one-scheduling.

As usual, the best solution is probably a mixed model of user and kernel threads. The threads are first scheduled by the thread library (user thread scheduling). Thereafter, the threads scheduled by the library are scheduled as kernel threads. Threads that are not compute-bound (e.g. performing I/O) are preempted by the scheduling mechanism of the library, while only compute-bound threads are scheduled by the kernel, thus enabling high-performance concurrent execution. In Pthread terminology, this model is called the many-to-one or some-to-one scheduling.

#### 3.5. Example Architectures

In Table 3, we present an overview of different systems which cost about or less than US\$ 60,000. Please note that all price information is selected from the different web sites of the different companies. Therefore, discounts and sales tax are not included.

More or less, we always tried to configure a standard system with a four GB harddisc and 128 MB of main memory. (This may appear not enough memory, but who buys memory from the system vendor anyway?). Prices are in US\$ (considering an exchange rate DEM 1.8/US\$ 1).

#### Sun Enterprise 450

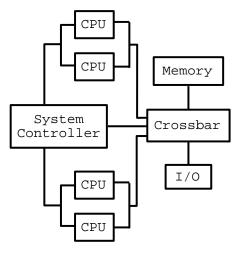

Figure 4 gives an overview of the Sun Ultra Enterprise 450 architecture. Up to four processors are connected via a crossbar to the UMA memory system and to the I/O system. The processors are managed via the system controler. On Sun workstations/servers, pthreads are available as mixed model implementation (Solaris 2.5 and above).

Figure 4: Basic Sun Enterprise 450 architecture

# Hewlett-Packard D-class/J-class architecture

In Figure 5, the basic architecture of D-class and J-class architure of Hewlett-Packard is shown. Up to two processors are connected via the memory bus to the UMA memory system and the I/O system. Similar to this architecture, the K-class servers can connect up to four processors. On HP-UX 10.30, pthreads are available as a kernel model. Older versions implement a user model.

Figure 5: Basic HP D-class/J-class architecture

ory systems, or even on workstation clusters. However, there is usually no access to a shared memory, thus limiting communication severely.

<sup>©</sup> The Eurographics Association and Blackwell Publishers 1998

#### Silicon Graphics Octane architecture

The processor boards of the SGI Octane architecture contain up to two processors and the UMA memory system. These boards are connected via a crossbar with the Graphics system and the I/O system (Figure 6). Pthreads are available for IRIX 6.3 and above, where pthreads are available as patch set for IRIX 6.2. On all implementations, a mixed model is used.

Figure 6: Basic SGI Octane architecture

# Silicon Graphics Origin200 architecture

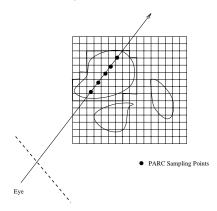

In contrast to the SGI Octane, no crossbar is used for the Origin200 architecture. The single tower configuration (up to two processors) connects the processors with the UMA memory system and the I/O system via a hub interconnect. For the four processors configuration, a "Craylink" interconnect links two two processors towers system to a Non-Uniform Memory Access (NUMA) system (Figure 7). In the case of the Origin200, a cache-coherent NUMA scheme is implemented, in order to provide a consistant memory view for all processors. Pthreads are available for IRIX 6.3 and above, where pthreads are available as patch set for IRIX 6.2. On all implementations, a mixed model is used.

Figure 7: Basic SGI Origin 200 architecture

| Vendor/Model       | CPU(s)      | [N]UMA | Interconnect            | Memory | Price |

|--------------------|-------------|--------|-------------------------|--------|-------|

| Sun/Enterprise 450 | 1 @250 MHz  | UMA    | crossbar @1.6 GB/s      | <4 GB  | 19K   |

|                    | 2 @250 MHz  | UMA    | crossbar @1.6 GB/s      | <4 GB  | 27K   |

|                    | 4 @250 MHz  | UMA    | crossbar @1.6 GB/s      | <4 GB  | 42K   |

|                    | 1 @300 MHz  | UMA    | crossbar @1.6 GB/s      | <4 GB  | 25K   |

|                    | 2 @300 MHz  | UMA    | crossbar @1.6 GB/s      | <4 GB  | 39K   |

|                    | 4 @300 MHz  | UMA    | crossbar @1.6 GB/s      | <4 GB  | 66K   |

| HP/J Class J2240   | 2 @236 MHz  | UMA    | bus @960 MB/s           | <1 GB  | 32K   |

| HP/D Class D370    | 1 @160 MHz  | UMA    | bus @960 MB/s           | <1 GB  | 29K   |

|                    | 2 @160 MHz  | UMA    | bus @960 MB/s           | <1 GB  | 39K   |

| HP/D Class D380    | 1 @180 MHz  | UMA    | bus @960 MB/s           | <1 GB  | 31K   |

|                    | 2 @180 MHz  | UMA    | bus @960 MB/s           | <1 GB  | 44K   |

| SGI/Octane SE      | 1 @225 MHz  | UMA    | crossbar @1.6 GB/s      | <2 GB  | 24K   |

|                    | 2 @225 MHz  | UMA    | crossbar @1.6 GB/s      | <2 GB  | 30K   |

|                    | 1 @250 MHz  | UMA    | crossbar @1.6 GB/s      | <2 GB  | 30K   |

|                    | 2 @250 MHz  | UMA    | crossbar @1.6 GB/s      | <2 GB  | 42K   |

| SGI/Origin 200     | 1 @180 MHz  | UMA    | hub @1.28 GB/s          | <2 GB  | 16K   |

|                    | 2 @ 180 MHz | UMA    | hub @1.28 GB/s          | <2 GB  | 22K   |

|                    | 4 @ 180 MHz | ccNUMA | hub/craylink @1.28 GB/s | <4 GB  | 42K   |

Table 3: Systems overview.

# 4. Parallel Programming

#### A. Message Passing

In this part of the tutorial, we briefly introduce two message-passing libraries. First we discuss the Message-Passing Interface library - MPI<sup>39, 40</sup>, followed by the Parallel Virtual Machine library - PVM<sup>42, 10</sup>. A comparison of these libraries can be found in an article by G. Geist et al.<sup>43</sup>. All these papers can be found on the web, either at netlib, or at the respective homepages of the libraries.

#### 4.1. Message Passing Interface - MPI

MPI 1 (1994) (and later MPI 2 (1997)) is designed as a communication API for multi-processor computers. Usually, the functionality of MPI is implemented using a communication library of the vendor of the machine. Naturally, this vendor library is not portable to other machines. Therefore, MPI adds an abstraction level between the user and this vendor library, in order to guarantee the portability of the program code of the user.

Although MPI does work on heterogeneous workstation clusters, its focus is on high-performance communication on large multi-processors<sup>43</sup>. This results in a rich variety of communication mechanisms. However, the MPI API lacks dynamic resource management, which is necessary for fault tolerant applications.

In the following Sections, we introduce the main components of MPI. Furthermore, we briefly explain some MPI functions, which are used in Section 7.

# 4.1.1. Process Topology and Session Management

To tell the truth, their is no real session management in MPI. Each process of a MPI application is started independent from the others. At some point, the individual processes are exchanging messages, or are synchronized at a barrier. Finally, they shut-down, thus terminating the application. The distribution of the individual processes to the different processing entities (e.g. processors of a multi-processor) is handled by the underlying vendor library.

- int MPI\_Init(int \*argc, char \*\*\*argv); inializes process for MPI.

- int MPI\_Finalize(void); releases process from MPI.

Furthermore, the user can specify the process topology within a group (see Section 4.1.2). Besides creating a convenient name space, the specification can be used by the runtime system to optimize communication along the physical interconnection between the nodes<sup>39</sup>.

# 4.1.2. Grouping Mechanisms

A special feature of MPI is support for implementing parallel libraries. Many functions are provided to encapsulate communication within parallel libraries. These functions define a

group scope for communication, synchronization, and other related operations of a library. This is done by introducing the concepts of communicators, contexts, and groups.

Communicators are the containers of all communication operations within MPI. They consist of participants (members of groups) and a communication context. Communication is either between members of one group (intracommunication), or between members of different groups (inter-communication). While the first kind of communication provides point-to-point communication and collective communication (such as broadcasts), the second kind only allows point-to-point communication. After initializing MPI for a process, two communicators are predefined. The MPI\_COMM\_WORLD communicator includes all processes which can communicate with the local process (including the local process). In contrast, the MPI\_COMM\_SELF communicator only includes the local process.

A group defines the participants of communication or synchronization operations. They define a unique order on their members, thus associating a rank (identifier of member within the group) to each member process. The predefined group MPI\_GROUP\_EMPTY defines an empty group.

The following functions provide information on a group or its members.

- int MPI\_Comm\_size(MPI\_Comm com, int\* nprocess); returns the number of participating processes of communicator com.

- int MPI\_Comm\_rank(MPI\_Comm com, int\* rank); returns rank of calling process.

A context defines the "universe" of a communicator. For intra-communicators, they guarantee that point-to-point communication does not interfere with collective communication. For inter-communicators, a context only insulates point-to-point communication, because collective operations are not defined.

#### 4.1.3. Communication

There are two different communication methods. Group members can be either communicate pairwise, or they can communicate with all members of the group. The first method is called point-to-point communication, the second method is called collective communication. Furthermore, a communication operation can be blocking (it waits until the operation is done) or non-blocking (it does not wait).

#### **Point-To-Point Communication**

This class of communication operation defines communication between two processes. These processes can be either members of the same group (intra-communication), or they are members of two different groups (inter-communication). However, we only describe systems with one group (all processes). Therefore, we only use intra-communication.

Usually, a message is attached to a message envelope. This envelope identifies the message and consist of the source or destination rank (process identifier), the message tag, and the communicator.

For blocking communication, the following functions are available:

- int MPI\_Send(void \*buf, int n, MPI\_Datatype dt, int dest, int tg, MPI\_Comm com); - sends the buffer buf, containing n items of datatype dt to process dest of communicator com. The message has the tag tg.

- int MPI\_Recv(void \*buf, int n, MPI\_Datatype dt, int source, int tg, MPI\_Comm com); - receives the message tagged with tg from process source of communicator com.

The used buffer buf consist of n items of the datatype dt.

These functions are specifying the *standard* blocking communication mode, where MPI decides if the message is buffered. If the message is buffered by MPI, the send call returns without waiting for the receive post. If the message is not buffered, send waits until the message is successfully received by the respective receive call. Besides this *standard mode*, there are *buffered*, *synchronous*, and *ready modes*. More information on these modes can be found in the MPI specification papers<sup>39, 40</sup>.

For non-blocking communication MPI\_Isend and MPI\_Irecv are provided for *intermediate* (I) communication. For *buffered*, *synchronous*, or *ready* communication modes, please refer to the MPI papers. After calling these functions, the buffers are send (or set while receiving). However, they should not be modified until the message is completely received.

- int MPI\_Isend(void \*buf, int n, MPI\_Datatype dt, int dest, int tg, MPI\_Comm com, MPI\_Request\* req); sends the buffer buf, contain n items of datatype dt to process dest of communicator com. The message has the tag tg.

- int MPI\_Irecv(void \*buf, int n, MPI\_Datatype dt, int source, int tg, MPI\_Comm com, MPI\_Request\* req);

receives the message tagged with tg from process source of communicator com. The used buffer buf consist of n items of the datatype dt.

In addition to the blocking send and receive, the request handle req is returned. This handle is associated with a communication request object - which is allocated by these calls - and can be used to query this request using MPI\_Wait.

int MPI\_Wait(MPI\_Request\* req, MPI\_Status \*stat);

waits until operation req is completed.

The last call we describe for point-to-point communication is MPI\_Iprobe. This call checks incoming messages if they match the specified message envelope (source rank, message tag, communicator), without actually receiving the message.  int MPI\_Iprobe(int source, int tg, MPI\_Comm com, int\* flag, MPI\_Status\* stat); - checks incoming messages. The result of the query is stored in flag.

If flag is set true, the specified message is pending. If the specified message is not detected, flag is set to false. The source argument of MPI\_Iprobe may be MPI\_ANY\_SOURCE, thus accepting messages from all processes. Similarly, the message tag can be specified as MPI\_ANY\_TAG. Depending on the result of MPI\_Iprobe, receive buffers can be allocated and source ranks and message tags set.

#### **Collective Communication**

Collective Communication is only possible within a group. This implements a communication behavior between all members of the group, not only two members as in point-to-point communication.

We concentrate on two functions:

- int MPI\_Barrier(MPI\_Comm com); blocks calling process until all members of the group associated with communicator com are blocked at this barrier.

- int MPI\_Bcast(void \*buf, int n, MPI\_Datatype dt, int root, MPI\_Comm com); - broadcasts message buf of n items of datatype dt from root to all group members of communicator com, including itself.

While the first call synchronizes all processes of the group of communicator com, the second call broadcasts a message from group member root to all processes. A broadcast is received by the members of the group by calling MPI\_Bcast with the same parameters as the broadcasting process, including root and com. Please note that collective operations should be executed in the same order in all processes. If this order between sending and receiving broadcasts is changed, a deadlock might occur. Similarly, the order of collective/point-to-point operation should be the same too.

# 4.2. Parallel Virtual Machine - PVM

While MPI was designed for message-passing on multi-processors, PVM was originally intended for message-passing within a heterogeneous network of workstations. In order to guarantee interoperability between independent computers, the concept of a virtual machine was introduced. While MPI supports only portability (a MPI-based application can be compiled on any system) but not interoperability, PVM processes can even communicate with processes build on completely different machines. Furthermore, processes can be started or terminated dynamically from a master process§, thus enabling dynamic resource management and fault tolerant applications.

<sup>§</sup> Functions to start or terminate processes are integrated in MPI

Generally, a parallel application using PVM3 is split into a master process and several slave processes. While the slaves do the actual work of the task, the master distributes data and sub-tasks to the individual slave processes. Finally, the master synchronizes with all slaves at a barrier, which marks the end of the parallel processing.

Before starting the parallel sessions, all designated machines of the cluster need to be announced in a *hostfile*. Furthermore, PVM demons must run on these machines. After running of the parallel sessions, all PVM demons (virtual machines) are shut down.

After this initialization, the master starts its execution by logging on to the running parallel virtual machine (PVM demon). Thereafter, it determines the available hardware configuration (number of available machines (nodes), ...), allocates the name space for the slaves, and starts these slaves by assigning a sub-task (program executable). After checking if all slaves are started properly, data is distributed (and sometimes collected) to the slaves.

At the end of the parallel computation, results are collected from the slaves. After a final synchronization at a common barrier, all slaves and the master log off from the virtual machine.

Next, we briefly introduce some commands for the process control. Furthermore, we introduce commands for distributing and receiving data. For details, please refer to the PVM book<sup>42</sup>.

#### **PVM Process Control**

- int pvm\_mytid(void); logs process on to virtual machine

- int pvm\_exit(void); logs process off from virtual machine.

- int pvm\_config(int\* nproc, ....) determines number of available nodes (processes), data formats, and additional host information.

- int pvm\_spawn(char \*task, ...) starts the executable task on a machine of the cluster.

- int pvm\_joingroup(char \*groupname); calling process joins a group. All members of this group can synchronize at a barrier.

- int pvm\_lvgroup(char \*groupname); leaving the specified group.

- int pvm\_barrier(char \*groupname); wait for all group members at this barrier.

- int pvm\_kill(int tid) kill slave process with identifier tid.

#### **PVM Communication**

int pvm\_initsend(int opt) - initializes sending of a message.

- int pvm\_pkint(int\* data, int size, ..); encodes data of type int<sup>¶</sup> for sending.

- int pvm\_send(int tid, int tag, ..); sends data asynchronous (does not wait for an answer) to process tid with specified tag.

- int pvm\_bcast(char\* group, int tag); broadcasts data asynchronously to all group members.

- int pvm\_mcast(int\* tids, int n, int tag); broadcasts data synchronously to n processes listed in tids.

- int pvm\_nrecv(int tid, int tag); non-blocking (does not wait if message has not arrived yet) receiving of message.

- int pvm\_recv(int tid, int tag); blocking receiving of message tag.

- int pvm\_upkint(int\* data, int size, ..); decodes received data of type int.

There is only one active message buffer at a time. This determines the order of initialization, coding, and sending of the message.

#### **B. Pthread Programming**

There are quite a number of thread models around, like the mthread package<sup>118</sup> of the University of Erlangen-Nürnberg, the dots package<sup>12</sup> of the University of Tübingen, the Compiler-Parallel-Support package of HP/Convex. There are NT-threads, Solaris-threads, and last but not least there is the IEEE POSIX thread standard (pthreads). In this tutorial, we will focus only on pthreads. Furthermore, all the examples are tested on SGI's implementation of pthreads (available for IRIX 6.x and up).

The pthread standard defines an "Application Programming Interface" (API), as specified by POSIX standard 1003.1, or more specific: ISO/IEC 9945-1:1996 (ANSI/IEEE Std 1003.1, 1996 Edition). However, this standard does not define a particular implementation of this standard. Therefore, many definitions are opaque to the user, e.g. thread mapping, data types, etc...

The following text only gives a more or less brief introduction intro pthread programming. Advanced features like real-time scheduling or attribute objects are only briefly mentioned or even completely ignored. For a more complete introduction into those topics, please refer to the books<sup>14, 87, 64, 57, 90</sup> listed in Section 8.

#### 4.3. Concurrency

There are some differences between programming of sequential programs and concurrent (parallel) programs. It is very important to realize that concurrent programs can behave completely differently, mainly because the notion of

<sup>¶</sup> There are commands for other data types, such as byte, double, as well

a sequence is not really available on the process level, although it is available on thread the level.

First of all, the **order of sequential programs** is determined at all times. In parallel programs, however, it is not. There are no statements within the pthread standard which control the actual order pthreads are scheduled. Consequently, we cannot tell which pthread will be executed before the other pthread.

Second - **critical sections**. A sequential program does not need to make sure that data which is not completely changed might be already read in another part of the program, because a sequential program only performs one statement at a time. This is different with concurrent programs, where different threads might perform different statements at virtually the same time. Therefore, we need to protect those areas, which might cause inconsistent states, because the modifying thread is interrupted by a reading thread. These areas are called critical sections. The protection can be achieved by synchronizing the threads at the beginning of these critical sections.

Third - **error handling**. Another difference is error handling. While UNIX calls usually return an useful value, if execution was successful, a potential error code is returned to the general error variable errno. This is not possible using threads, because a second thread could overwrite the error code of a previous thread. Therefore, most pthread calls return directly an error code, which can be analyzed or printed onto the screen. Alternatively, the string library function char\* strerror(int errno);

returns an explicit text string according to the parameter errno.

# **4.4.** Controlling Pthreads

In this part, we discuss the life cycle of a pthread. The life cycle starts with the creation of the pthread, its work, and the end of its existence.

To start the life of a pthread, we need to execute the pthread\_create command:

where

- pthread\_id is the returned identifier of the created pthread,

- pthread\_attr\_t is the passed attribute structure. If NULL is passed, the default attributes are used.

- thread\_routine is the name of the function which is called by the created pthread, and

- arg is a pointer to the parameter structures for this pthread.

If this function returns error code 0, it was successful. If an error was encountered, the return code specifies the encountered problem.

If a pthreads needs to know its identity, this identity can be established using the call

```

pthread_t pthread_self(void);

```

where the pthread identifier of the current pthread is returned. However, the pthread identifier of another pthread is only known by its caller. If this information is not passed to the particular pthread, this pthread does not know the identifier of the other pthread.

Similar to the last call,

determines if two pthread identifiers are referring to the same pthread. If t1 is equal t2 a nonzero value will be returned ("True"); if they are not equal, zero will be returned ("False").

The life of a pthread usually terminates with a

```

int pthread_exit(void *ret_val);

```

call. Although the pthread is terminated, the resources used by this pthread are still occupied, until the pthread is detached. Using the command

```

int pthread_detach(pthread_tpthread_id);

```

explicitly detaches a pthread, telling the operating system that it can reclaim the resources as soon as the pthread terminates.

If a pthread A needs to wait for termination of pthread B, the command

can be used. As soon as pthread B terminates, it joins pthread A, which is waiting at the pthread\_join command. If pthread B is returning a result using the pointer ret\_val, this pointer is accessible via ret\_val of the pthread\_join command. If ret\_val is set to NULL, no return value will be available. pthread\_join implicitly detaches the specified pthread.

An example for pthread creation can be found as listing 1 in Section 4.7.1.

# 4.5. Pthread Synchronization

One of the most important topics in thread programming is synchronization. Different resources (e.g. variables, fields, etc.) are shared by different threads. Therefore, the access to these resources needs to be protected. Usually, this protection for MUTual EXclusion is done by a mutex. However, other synchronization mechanisms are known, such as conditions and barriers.

#### 4.5.1. Mutex Synchronization

A mutex protects a critical section in a program. Considering a scenario, where rendering information is stored in a special data structure - e.g. a FIFO queue -, and two threads try to read information from that data structure, obviously, the access to this data structure is a critical section and the access must be limited to one thread at the time. Therefore, the data structure must be protected by a mutex.

#### Initialization

After memory allocation of the mutex structure, it must be initialized. For static allocation, we can simply assign the preprocssor macro PTHREAD\_MUTEX\_INITIALIZER to the mutex.

In most cases, however, we dynamically allocate a mutex. For these cases, we can use pthread\_mutex\_init to initialize the allocated mutex structure. The second parameter of this command is used to specify a mutex attribute object. This attribute object is not frequently used. Therefore, we pass NULL.

If no pthread is locking the mutex, we can destroy it using pthread\_mutex\_destroy before releasing the mutex structure memory. If the mutex is statically allocated and initialized, the explicit destruction of the mutex is not necessary.

#### Using a Mutex

Before entering a critical section in a parallel program, we need to lock the associated mutex using pthread\_mutex\_lock. If the mutex is already locked, the current pthread will be blocked, until the mutex is unlocked by the other pthread. The behavior if a pthread tries to lock a mutex which is already locked by the very same pthread is not defined. Either an error code will be returned, or this pthread will end up in a deadlock.

In case you do not want to wait on an already locked mutex, you can use pthread\_mutex\_trylock. This

call returns EBUSY in case that the specified mutex is already locked by another pthread. At the end of a critical section you need to unlock the locked mutex using pthread\_mutex\_unlock.

An example for pthread mutexes can be found as listing 2 in Section 4.7.2.

#### Semaphores

Semaphores is a concept which is more or less a generalization of a mutex. While a mutex only is a binary representation of the state of a resource, a semaphore can be used as a counter ("counting semaphores"). Although the pthread standard does not specify semaphores, the POSIX semaphores can be used.

#### 4.5.2. Condition Synchronization

While mutexes protect a critical section of a program, conditions are used to send messages on the state of shared data. Considering the classic user/producer problem, the producer signals a condition to the users that it has produced data which can be digested by the users.

Dave Butenhof<sup>14</sup> says that

condition variables are for signaling, not for mutual exclusion.

#### Initializing

Similar to the mutex initialization, static and dynamic allocated condition structures need to be initialized using the respective commands. For our use, we always pass NULL to the condattr parameter. Further discussion of the attribute features can be found in Butenhofs book<sup>14</sup>.

After use, the condition structures need to be destroyed before releasing the associated memory.

#### Using conditions

Note that conditions are always associated with a mutex, where pthreads waiting on the same condition must use the very same mutex. It is not possible to combine two mutexes with one condition, while it is possible to combine two (or more) conditions with one mutex.

Before entering the wait stage using pthread\_cond\_wait or pthread\_cond\_timedwait, the associated mutex must be locked. This mutex is automatically unlocked while waiting on that condition and re-locked before leaving the wait stage. Similar, a signaling pthread needs to lock the mutex before signaling the waiting pthread (see listing 3, Section 4.7.3).

If you consider a waiting pthread A and a signaling pthread B, A will lock the associated mutex mA before entering the wait stage of condition cA. Immediately before blocking pthread A, the system unlocks mutex mA. Later, pthread B locks mutex mA in order to signal pthread A the condition cA. The signal is received by pthread A, which tries to lock mutex mA. After unlocking mutex mA by pthread B, pthread A locks mutex mA and returns from the pthread\_cond\_wait to the user's code. Thereafter, the user unlocks mutex mA.

Another important note is that pthreads might wake up without getting the proper signal for various reasons. Therefore, we need to use a shared predicate which is set if there is a proper wake-up signal. If this predicate is not set, the waiting pthread will wait again until it receives the proper signal.

In some situations it is useful to limit the waiting time by a timeout. In these cases, the maximum waiting time can be specified by the exp parameter of the pthread\_cond\_timedwait command. It will return with the value ETIMEDOUT if the pthread does not receive the expected signal within the timeout limit.

The pthread mechanism for waking-up pthreads waiting at a condition is pthread\_cond\_signal and pthread\_cond\_broadcast. While the first one only wakes up the first pthread waiting at that condition, the latter wakes up all pthreads waiting at that condition.

Please note, if no pthread is waiting at a condition, this condition will simply die away. Furthermore, if a pthread starts waiting at this condition shortly after the wake-up signal/broadcast, it remains waiting for a signal which possibly never arrives.

An example for pthread conditions can be found as listing 3 in Section 4.7.3.

#### 4.5.3. Barrier Synchronization

The last presented synchronization concept is the barrier synchronization. Unfortunately, this concept is not part of the current pthread standard (1996), but it is on the draft list for the next version.

Generally, a barrier synchronization stops threads at this barrier, until the specified number of threads arrive. Thereafter, all threads proceed. There are different suggestions how to implement barriers in the current pthread standard. We will present two examples of an implementation. The first one implements a barrier synchronization at the end of the life cycle of the threads by joining them in a cascade (see listing 2 in Section 4.7.2). However, this method is not suited for a barrier synchronization which is not at the end of the life cycle of the pthreads, but in the middle of the working program. In addition, it has some structural limitations, because each pthreads in the cascade needs to know its successor's pthread identifier.

The second example is from Dave Butenhof book on POSIX threads<sup>14</sup>. In this example, every pthread which waits at a barrier is decrementing the waiting pthread counter and checks if more pthreads are expected to wait at this barrier. If no further pthread is expected to wait, it broadcasts the other waiting pthreads that the appropriate number of pthreads arrived at the barrier. If the number of waiting pthreads is not reached, this pthreads starts waiting for the broadcast. This implementation of a barrier can be found as listing 4, Section 4.7.4.

#### 4.6. Additional Topics

#### 4.6.1. Concurrent Memory Visibility

As mentioned earlier, programming concurrent (parallel) systems is quite different from programming sequential systems. This is especially true for the view of the memory we are using within our parallel program.

Modern processors are buffering data into caches of different sizes and different levels. If more than one processor is working for one program, different caches are storing information. Therefore, the information visible by one processors (in its cache) might be not the same as visible to another processor (in its cache or the main memory). This problem becomes even worse if NUMA memory architectures are used, because checking for changes in different caches and different memory hierarchies is much more difficult.

The pthread standard defines situations when the memory view of the different threads (possibly running on different processors) is equal, providing that the memory has not changed after these commands.

- After starting pthreads (pthread\_create), the started pthreads have the same memory view as their parent.

- After explicitly (pthread\_mutex\_unlock) or implicitly (conditions) unlocking mutexes, the pthreads

which are blocked at this mutex have the same memory view as the unlocking pthread.

- Furthermore, the memory view of terminated pthreads (canceled pthreads, exited pthreads, or simply returning from their thread function) is the same as of the pthread which joins the terminating pthreads.

- Finally, each pthread which is waked-up by a signaling or broadcasting pthread has the same memory view as the signaling or broadcasting pthread.

Apart from these situations, the same memory view can not be guaranteed. Although you might never encounter this problems on a particular system (it might be cachecoherent), you can never be sure.

#### 4.6.2. Cancelation

Usually, a thread is executing a particular part of the program until the task is done and the thread is either returning to its parent thread (main thread), or exits. However, there are situations where the task of the thread becomes dispensable. In those cases, it is useful to cancel this thread.

In general, we need the pthread identifier of the pthread to be canceled. Without this identifier, we cannot cancel the pthread. To cancel a pthread, we call pthread\_cancel(pthread\_id);.

There are three different cancelation modes the user can choose from. First, there is the DISABLED mode, where the cancel state is set to PTHREAD\_CANCEL\_DISABLE (the value of the cancel type will be ignored). In this mode no cancelation is possible. It becomes meaningful to prevent data corruption, while the pthread is changing data. In this cases, the pthread disables cancelation until it has finished the modification. Thereafter, it enables cancelation again. Cancel requests issued while the cancelation is disabled, are queued until the cancelation state is enabled again.

If the cancelation state is set to PTHREAD\_CANCEL\_ENABLE, we can choose from two cancelation types; PTHREAD\_CANCEL\_DEFERRED (the default) or PTHREAD\_CANCEL\_ASYNCHRONOUS. The second type indicates that the respective pthread should be canceled at any time from now. This might cause data corruption, deadlocks - pthreads which are locked at a mutex locked by the canceled pthread -, and so forth. This is really an emergency kind of cancelation. Better is the first cancelation type, which asks the

pthread to stop at the next cancelation point. At implicit cancelation points like pthread\_cond\_wait, pthread\_cond\_timedwait, or pthread\_join, the pthread cancel immediately after executing these commands. However, an explicit cancelation point can be set using pthread\_testcancel. If a cancel request is pending, the pthread returns the value PTHREAD\_CANCELED to a pthread which waits to join this pthread. If no cancel request is pending, the pthread\_testcancel command immediately returns. Besides these implicit or explicit cancelation points, there are library calls or system calls which are implicit cancelation points. Generally, these calls can introduce some blocking behavior and are therefore good candidates for cancelation. Please refer to one of the pthread books for a list of these calls.

Please note, enabling cancelation is not a cancelation point. Therefore, you need to explicitly set a cancelation point after enabling cancelation.

Another feature of cancelation is the specification of an cleaning-up handler for the pthread to be canceled. This cleaning-up handler can close files, release memory, repair data modifications, and so forth. Please refer to Butenhofs book<sup>14</sup> for more information on cleaning-up canceled pthreads.

#### 4.6.3. Hints

In this Section, we provide some tips and hints on common problems and usage of pthreads on some systems.

#### **Debugging**

- Thread races. Never count on an execution order of pthreads. Generally, we can not assume a certain executing order of pthreads. The standard does not completely control the actual scheduling of the physical system. Furthermore, after creation of a pthread, you cannot count that this pthread will start before another pthread created after the first pthread.

- Avoid potential deadlock situations. Well, this sounds

obvious. However, there are many unavoidable situations

which are potential deadlock situations. If you use mutex

hierarchies (lock one mutex after successfully locking a

first mutex), you need to consider a back-off strategy in

case that the second mutex locking will block the pthread,

which keeps the first mutex.

- **Priority inversion.** If you use real-time priority scheduling (see Section 4.6.4), your scheduling strategy (FIFO) might schedule a pthread to run which tries to lock a mutex, locked by a pthread preempted by the first pthread. Mutual exclusion and scheduling performing a kind of contradictory execution which can cause a deadlock.

- Sharing stacks. Pthread attributes (Section 4.6.4) enable the user to share stack memory. If the size of this stack

is too small for these pthreads, you will encounter some strange effects.

#### Performance

- Mutexes are not for free. You should always carefully decide if you use a "big mutex" protecting one big piece of code, or a number of mutexes protecting more fine granularly critical sections.

- IRIX Pthreads. The current implementation of pthreads on SGI workstations maps the pthreads on sproc lightweight processes of the operating systems. Furthermore, the system decides if it starts additional sproc for an additional pthread.

- In my experience, this does not work very well. Therefore, you can tell the operating system that your pthreads are compute-bound, by setting the environment variable PT\_ITC (setenv PT\_ITC). This usually results in starting enough sprocs for all processors.

- Solaris threads. On Solaris 2.5, threads are not timesliced. Therefore, we need to set the concurrency level to the number of started threads, in order to obtain a concurrent program execution. The respective command is thr\_setconcurrency(<nthreads>);.

I found a nice quote in Dave Butenhof's book for those who are getting frustrated while debugging a concurrent program:

Wisdom comes from experience, and experience comes from lack of wisdom.

#### 4.6.4. Further topics

In this tutorial, we do not provide material on all pthread topics. In my experience, I have never needed features like one-time initialization, real-time scheduling, thread-specific data, thread attributes, and so forth. However, there are situations where you might need this features. A discussion of these additional features can be found in Butenhofs book<sup>14</sup>.

#### 4.7. Example Code

This part contains example code for pthread programming. Please note that we denote the thread which starts all other threads as main thread. Naturally, this thread is considered as a pthread too. Furthermore, we use the term pthread for all threads started by the main thread using the command pthread\_create.

#### 4.7.1. Initializing Pthreads

The pthread program listed listing 1, starts five pthreads and passes a couple of values to the pthreads. Finally, the main pthread collects the pthread started first.

14, number of pthreads started (including the main thread).

- 16-19, type definition of parameter record passed to the started pthreads.

- 21-38, thread function which is executed by the started pthreads. The own pthread identifier is look up (27). After a short loop (28), the thread function tests if the current pthread is the main thread (30). All pthreads created by the main thread are terminated and return their number identifier (35).

- 48-63, PTHREADS 1 pthreads are started and a parameter record containing two parameters are passed to the pthreads; the current loop value (like a number identifier for the pthreads) and the pthread identifier of the main thread.

- 65-72, the four pthreads (PTHREADS 2) started last are detached from the main thread. After their termination, their resources are released to the operating system. If the main thread terminates before these pthreads, they terminate immediately (without completing their thread function).

- 74, the main thread executes the thread function (like the other pthreads).

75-76, the main thread joins with the first pthread started (and implicitly detaches this pthread, 75). The return value of the started pthread is returned in resp (75) and casted (76).

# 4.7.2. Mutex Example

The pthread program listed listing 2, starts five pthreads and passes a couple of values to the pthreads. Each started pthread tries to lock the mutex allocated and initialized by the main thread.

- 20-25, type definition of parameter passed to the pthreads.

- 27-63, thread function executed by the started pthreads. Each started pthread locks the shared mutex 100 times (32-557). After locking (36), it performs a loop (43) and unlocks the mutex (44-49). Finally, each started pthread terminates using pthread\_exit (60). In contrast to the mutex locking of the main pthread (105), the pthreads are using trylock and count the unsuccessful tries (38-41).

- 72-83, a common mutex is allocated (72-76) and initialized (78-83).

- 85-103, five pthreads are started and the respective data is passed to them (96).

- 105-117, the mutex is locked by the pthread (105-110). Please note that this mutex is not necessarily locked by the main thread first. The pthread standard does not specify a scheduling/execution order (see 4.6.3 thread races). After successful locking, the main thread executes a loop (111) and unlocks the mutex (112-117).

- 119-129, the main thread joins with all started pthread in the order they were created. If a pthread created later terminates before an earlier pthread, it is not joined until all pthreads created earlier were joined. This is a cascade implementation of a barrier. The main thread does not proceed

until all started pthreads are joined. Please note that after the presented kind of barrier synchronization, no pthreads are running anymore.

131-137, the mutex is released.

#### 4.7.3. Condition Example

The pthread program listed listing 3, starts two pthreads and passes a couple of values to the pthreads. Finally, the main pthread collects the started pthreads. The pthreads are alternating processing a shared variable using conditions to signal the state of the variable to the pthread.

18-24, type definition of shared data passed to the pthreads.

26, shared data definition.

39-72, allocates and initializes mutex (43-51) and conditions (53-70).

74-113, producer pthread. After waiting for two seconds (82) in order to make sure that consumer pthread waits at the condition, the producer locks the mutex (87-90), manipulates the shared data, setting the predicate to 0, marking that it has been processed by the producer (91-92), and signals to the consumer that the shared data is ready to process (93-96). Thereafter, the producer waits until the data is consumed by the consumer pthread (98-103). Each time the producer is waked up by a signal (99), it checks if the predicate is correct. If not, it continues waiting (98,103). This is to prevent wrong wake-ups of the waiting pthread. After waiting of the pthread at this condition, the mutex is unlocked (107-110). Please note that while waiting for the signal (99), the mutex is unlocked by the system and re-locked before returning to the user code.

115-151 consumer pthread. Similar to the producer pthread, the consumer locks the mutex (124-127) and waits at the condition for the proper signal (128-133). If a wrong signal is received which waked-up the consumer, the predicate is not set properly. Therefore, we continue waiting (128, 133). After successful receiving the proper signal, the consumer consumes the shared data (135), sets the predicate (136), and signals the consumption to the producer pthread (139-142). Thereafter, it unlocks the mutex (144-147) and continues waiting (124) for new data. Please note that the mutex is locked while producer/consumer are manipulating the shared data. The mutex is released by the pthreads, while they are waiting at the condition. If the mutex is unlocked while manipulating the data, a deadlock is usually the result, because the later signal might be received by the other pthread. Due to scheduling, it is possible that the pthread just waked-up by a wrong signal, therefore misses the correct signal.

159-166, producer and consumer are started. The producer/consumer cycles is performed 200 times. (Actually, only pointers to data structures should be passed. An integer does not always fit into the memory space of a pointer.

170-177, both pthreads are collected by the main thread. 179-193, resources are released.

#### 4.7.4. Barrier Example

This Section describes the barrier example of the book by Dave Butenhof $\|$ .

Three functions are defined; barrier\_init and barrier\_destroy define the initializing and destructor functions of the barrier. The function barrier\_wait defines the entrance to the barrier. The pthreads at this barrier wait until a specified number of pthreads has arrived. This number is specified in barrier\_init.

1-42 barrier header file barrier.h.

43-186 barrier code file barrier.c.

19-26 type definition of barrier.

72-88 barrier\_init. This function initializes the barrier barrier (72). The number of pthreads which need to wait at this barrier is specified with count (72,76). In 77, cycle is initialized. This variable is used to filter wrong wake-up signals. Finally, the barrier is made valid in 86.

93-125 barrier\_destroy. This function removes the barrier barrier (93). After checking if the barrier is valid (97), the barrier access mutex is locked (100). If any pthreads are still waiting at this barrier (108), this function is aborted (110). If no pthreads are waiting, the barrier is invalidized (113), the access mutex unlocked and released, and the condition is removed (122,123).

132-186 is the actual barrier function. The pthreads which enter this function are blocked (169) until the it receives a signal and the cycle has changed, since the pthread has entered this function. If the pthread which has just entered the barrier\_wait function is the pthread all the other pthreads are waiting for, it changes the cycle (146), resets the counter (147), and broadcasts to all waiting pthreads that it has arrived (148).

D. Butenhof, PROGRAMMING with POSIX THREADS, (page 245). (C) 1997 Addison Wesley Longman Inc., Reprinted by permission of Addison Wesley Longman.

#### **Listing 1 - Initializing Pthreads**

```

1

* create.c

* starting and terminating pthreads

#include <stdio.h>

#include <stdlib.h>

9 #include <limits.h>

10 #include <string.h>

12 #include <pthread.h>

14

#define NO_PTHREADS 6

15

16

typedef struct {

17

pthread_t main;

int pthread_no;

} ident_t;

18

19

void* thread_function(void* arg)

21

22

int     i;

ident_t* info = (ident_t*) arg;

23

24

25

pthread_t self;

26

27

self = pthread self();

for (i=0; i<INT_MAX/100; i++);

29

30

if (pthread_equal(self,info->main)) {

fprintf(stderr,"Current pthread is main thread.\n");

31

} else {

32

33

pthread_exit((void*) &(info->pthread_no));

35

36

37

return NULL;

38

39

int main(void)

41

42

int

i.rc;

43

44

45

*res;

void *resp;

pthread_t ids[NO_PTHREADS+1];

ident_t infos[NO_PTHREADS+1];

void

47

48

ids[0]= pthread_self();

49

infos[0].pthread_no = 0;

infos[0].main = pthread_self();

for (i=1; i<=NO_PTHREADS; i++) {</pre>

50

51

52

infos[i].pthread_no = i;

infos[i].main = pthread_self();

rc = pthread_create(&ids[i], NULL, thread_function,

53

54

55

56

57

58

59

(void*) &(infos[i]));

if (rc)

fprintf(stderr, "ERROR - while creating pthread %d: %s\n",

infos[i].pthread_no, strerror(rc));

exit(-1);

60

61

fprintf(stderr, "Main: Thread %d started.\n",

62

infos[i].pthread_no);

63

```

```

for (i=2; i<=NO_PTHREADS; i++) {

rc = pthread_detach(ids[i]);

if (rc) {

66

67

68

fprintf(stderr, "ERROR - while detaching pthread %d: %s\n",